## **MIMD Architectures**

- Further Division of MIMD

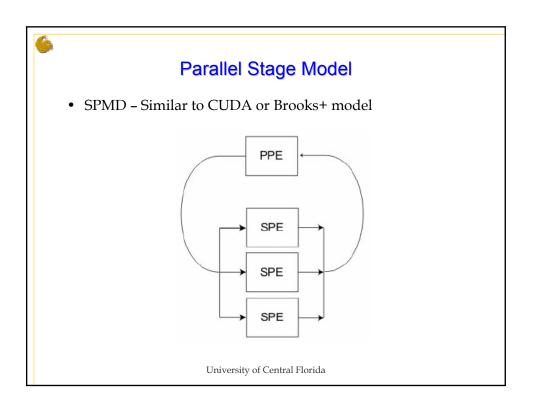

- Single Program, Multiple Data Stream (SPMD)

- Exploit Data-Level Parallelism

- Difference between SIMD: no lockstep

- In GPU, SIMD in a warp/cluster; SPMD among multiple warps/clusters

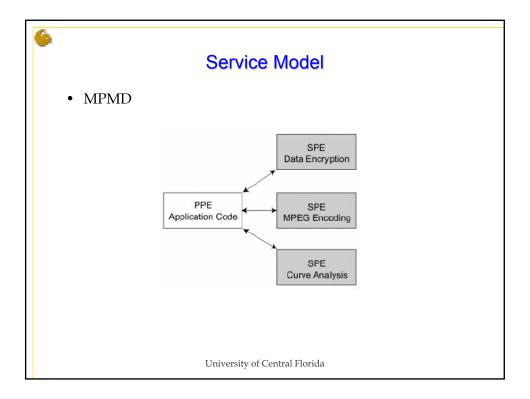

- Multiple Program, Multiple Data Stream (MPMD)

- Exploit Function/Task-Level Parallelism

- E.g., Master/worker

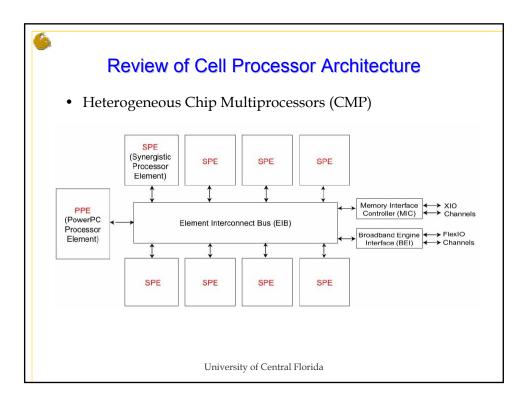

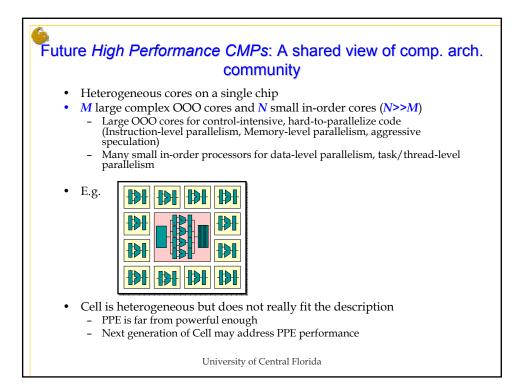

- Cell processors

- Supports MPMD

- In each SPU, SIMD execution exploits data-level parallelism

- Multiple SPUs can execute *different* codes.

University of Central Florida