### **Module Overview**

- CAL Kernel Programming APIs

- Overview of AMD IL

- Overview of AMD GPU ISA

### **CAL Kernel Programming APIs**

- AMD Brook+

- DirectX High Level Shading Language (HLSL)

- AMD Intermediate Language (IL)

- AMD GPU-specific Assembly Instruction Set (ISA)

### AMD Brook+

- 'C' with Streaming Extensions

- Includes

- Kernel programming interface

- Runtime implementation

Transparent to application programmer

Supports multiple runtimes

– Runtime API

Simple and small API for basic operations

Provides only high-level control over stream data

## DirectX High Level Shading Language (HLSL)

- 'C' for GPU Programming for 3D applications

- Includes

- Kernel Programming Interface

- Runtime provided by associated runtime library (DirectX)

- Front-end compiler provided by Microsoft (fxc)

- Back-end code generation and optimization done by GPU vendors

- Original BrookGPU included as DirectX runtime

- Generate HLSL for Brook kernels

- Invoke DirectX runtime calls for stream management and kernel invocation, etc

### **AMD Intermediate Language**

- Psuedo-assembly interface

- Interface is Architecture Independent

- Includes graphics-ish commands as well

- Evolves with GPU evolution

- Specifications available with the SDK installation

### AMD GPU ISA

- True GPU assembly

- Interface and Implementation is *Architecture Dependent*

- Exposes the GPU architecture completely

- Provides insight into GPU architecture and expected performance

- No optimizations done by the assembler on specified ISA

- Not expected to use directly for application development

- Very useful for performance profiling

- Useful for debugging programs

### Overview of AMD IL

### AMD IL Interface

- An IL program consists of

- Versioning information, declarations, etc

- Registers (operands, temporaries and results)

- Instructions

- IL registers are 4-component vectors

- IL instructions that accept vectors by default perform vector instructions

- Current and future GPUs have superscalar units so scalar instructions are encouraged

- ⇒Use masking operators when vector instructions are not needed

- ⇒The compiler will optimize the generated code appropriately

### AMD IL – Data Types

- IL is a type-less language

- Registers do not have specific types

- Can be used to store 32-bit integers, floats, and 64-bit double precision values

- Types are defined by the instructions, e.g.

IMUL, UMUL, MUL and DMUL

correspond to multiplication of

signed integers, unsigned integers, floats and doubles respectively

### AMD IL – Instruction Syntax

```

<instr>[_<ctrl>][_<ctrl(val)>]

[<dst>[_<mod>][.<write-mask>]]

[, <src>[_<mod>][.<swizzle-mask>]]...

```

Items within <> are replaced by specific words or phrases. For example, <instr> could be replaced by mov.

When more than one item of the same type exists, for example <src>, a zero-based number is appended to the item name. For example, for 2-input instructions the sources (inputs) would be labeled src0 and src1.

Items within square brackets, [], are optional.

Items within braces,  $\{\}$ , represent a choice-grouping. For example,  $\{x | y | z | w\}$  means to choose x, y, z or w.

An ellipsis, ..., represents a list of alternatives having the same format as the first alternative in the list.

### **Important ALU Instructions**

mul dst, src0, src1

dst = src0 \* src1

MAD – Multiplication of two registers and addition with third – More efficient as it performs 2 vector instructions in 1 cycle

```

mad[_ieee] dst, src0, src1, src2

```

```

dst = src0 * src1 + src2

```

### **Important ALU Instructions**

DIV – Division of two registers

```

div_zeroop(op) dst, src0, src1

```

dst = src0 / src1

zeroop() decides value of output if divisor is zero, e.g.

fltmax, zero, infinity, inf\_else\_max

RCP – Reciprocal

rcp\_zeroop(op) dst, src0

dst = 1/src0.w

SQRT – Square Root

sqrt dst, src0

dst = sqrt(src0.w)

### **IL Registers**

### IL provides registers for various tasks

| Register | Description  | Need to<br>declare | Example                            |

|----------|--------------|--------------------|------------------------------------|

| r#       | Temporary    | No                 | mad r0, r0, r0, r0                 |

| cb#[#]   | Const buffer | Yes                | mov o0, cb0[0]                     |

| v0       | Position     | Yes                | <pre>mul o0, v0.xyxx, cb0[0]</pre> |

| 0#       | Output       | Yes                | mov o0, v0.xyxx                    |

### **Reading Inputs - Samplers**

- Handle used to "Sample" or read from input buffers (textures in graphics)

- specify the buffer from which to read

- the address within this buffer 2-tuple for 2D buffers

- use sampling operator

```

C

// Buffer A, Address (x, y), Operator [][]

float temp = A[x][y];

Prook |

```

Brook+

```

// Buffer A, Address vector reg.xy, Operator []

float templ = A[reg.xy];

```

### IL

```

// Buffer resource 0, Address vector v0.xy, Operator

// sample_resource(#)_sampler(#)

sample_resource(0)_sampler(0) r0, v0.xy

```

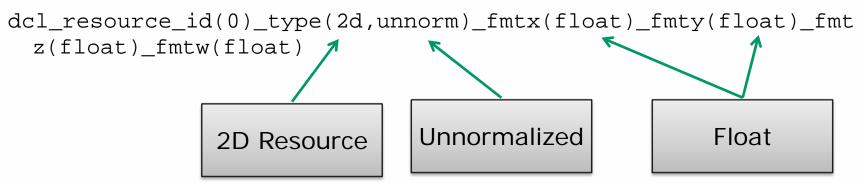

### **Reading Inputs - Samplers**

- Both the sample operator and output register are type-less

- The data format and sampling mode needs to be specified in the kernel for each sampler

### e.g.

- Type of resource (1d vs 2d) specified

- Type of address (normalized vs unnormalized) specified

- Normalized uses coordinates in [0..1] range

- Unnormalized uses coordinates in [0..n-1] range

# Register Modifiers, Masks and Swizzles <instr>[\_<ctrl>][\_<ctrl(val)>] Write Mask [<dst>[\_<mod>][.<write-mask>]] Write Mask [, <src>[\_<mod>][.<swizzle-mask>]]... Source Modifier Destination Modifier Source Modifier Swizzle Mask

### **Source Modifiers**

| Modifier            | Description                                                                                                          | Example                              |

|---------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| _invert             | Invert components ( 1- x )                                                                                           | add r0, r1_invert, r2                |

| _bias               | Elements are biased ( x – 0.5 )                                                                                      | add r0, r1, r2_bias                  |

| _x2                 | Multiply elements by 2.0                                                                                             | add r0, r1, r2_x2                    |

| _bx2                | Signed scaling. Combined bias and x2 modifiers.                                                                      | add r0, r1, r2_bx2                   |

| _sign               | Signs Elements<br>Elements less then 0 become -1<br>Elements equal to 0 become 0<br>Elements greater then 0 become 1 | mov r0, r1_sign                      |

| _divcomp(type)      | Performs division based on <i>type</i> .<br><i>type</i> : y, z, w, unknown                                           | texld_stage(0) r0,<br>vT0_divcomp(y) |

| _abs                | Takes the absolute value of elements.                                                                                | mov r0, r1_abs                       |

| _neg( <i>comp</i> ) | Provides per element negate                                                                                          | mov r0, r1_neg(xw)                   |

### **Destination Modifiers**

| Modifier                               | Description                       | Example                                     |

|----------------------------------------|-----------------------------------|---------------------------------------------|

| _x2<br>_x4<br>_x8<br>_d2<br>_d4<br>_d8 | Shift scale modifiers             | add_x2 r0, r1, r2                           |

|                                        | Saturate or clamp result to [0,1] | add_sat r0, r1, r2<br>add_x2_sat r0, r1, r2 |

### Write Masks

Mask a destination element using specified flag

reg. $\{x|_|0|1\}\{y|_|0|1\}\{z|_|0|1\}\{w|_|0|1\}$

- -Letter (x, y, z, w) => element to be written

- Underscore (\_) => element *not* to be written

- Zero (0) or One (1) => element forced to zero or one

- Omitting => underscore

E.g.

```

mov r0.x_zw, r1

```

```

mov r0.x_01, r1

```

### Swizzle-mask

Manipulate the default positions of elements in a register to be used as a source/destination

reg.{x|y|z|w|0|1}{y|z|w|x|0|1}{z|w|x|y|0|1}{w|x|y| z|0|1}

– Swizzle mask is position dependent

- Letter (x, y, z, w) => element to be read/written

- Zero (0) or One (1) => element forced to zero or one

- Omitting => default value

E.g.

mov r0, r1.yz ; same as mov r0, r1.yzzw

mov r0, r1.yzx1 ; force r0.w to be 1

### Comments

Semi-colon used for comment

e.g.

; this is a comment

mov r0, r1 ; this is another comment

### AMD GPU ISA

- Reviewing assembly is handy for performance profiling and debugging

- CAL provides interfaces to dump dis-assembly from CALimage

calclDisassembleImage

void calclDisassembleImage(const CALimage image, CALLogFunction logfunc);

• Disassembles the CAL image

calclDisassembleObject

void calclDisassembleObject(const CALobject\* obj, CALLogFunction logfunc);

Disassembles the CAL object

### AMD GPU ISA

- Disassembler

- Both outputs the disassembled ISA on a line-by-line basis

- Uses application specified log function

```

typedef void (*CALLogFunction)(const char* msg);

```

```

void disasm(const char *msg) {

```

```

fprintf(stderr, "%s\n", msg);

```

```

}

```

calclDisassembleImage(image, disasm);

calclDisassembleObject(object, disasm);

- Command line utilities amudisasm, amuasm

- Dis-assemble a given binary image

- Assemble a given text GPU ISA kernel

### OUTPUT: R600 ISA INPUT: AMD IL Kernel \_ B 🗙 GPU ShaderAnalyzer - IL File Edit Help Object Code Source Code Ŧ Format Radeon HD 2900 (R600) Assembly -Function ; ----- PS Disassembly -----1 // Enter your shader in this window 00 ALU: ADDR(32) CNT(4) KCACHEO(CB0:0-15) 2 il ps 2 0 3 dcl\_input\_interp(linear) v0 0 x: MUL RO.x, RO.x, KCO[0].x 4 dcl output generic o0 y: MUL RO.y, RO.y, KCO[0].y 5 dcl\_cb cb0[1] z: MUL RO.z, RO.y, KCO[0].z 6 mul o0, v0.xy, cb0[0] w: MUL RO.w, RO.y, KCO[0].w 7 ret\_dyn 01 EXP\_DONE: PIXO, RO 8 end END OF PROGRAM > > < < Compiler Statistics (Using Catalyst 7.12) GPR Min Max Avg Est Cycles(Bi) ALU:TEX(Bi) Est Cycles(Tri) ALU:TEX(Tri) Est Cycles(Aniso) ALU:TEX(Aniso) BottleNeck(Aniso) BottleNeck(Aniso) Pixell(Clock(Bi) Pixell(Clock(Cri) Pixell(Clock(Aniso) Scrat Name Radeon 9700 N/A Radeon x800 N/A Radeon x850 N/A N/A N/A N/A N/A Radeon x1800 N/A Radeon x1300 N/A Radeon x1600 N/A Radeon x1900 N/A Radeon HD 2900 1.00 1.00 1.00 1.00 1.00 EXP EXP 16.00 16.00 16.00 2 1.00 1.00 1.00 1.00 Radeon HD 2400 2 1.00 1.00 1.00 1.00 1.00 1.00 1.00 1.00 1.00 EXP EXP EXP 4.00 4.00 4.00 Radeon HD 2600 2 2.00 2.00 2.00 2.00 2.00 2.00 2.00 2.00 2.00 EXP EXP EXP 4.00 4.00 4.00 Radeon HD 3870 2 1.00 1.00 1.00 1.00 1.00 1.00 1.00 1.00 1.00 EXP EXP EXP 16.00 16.00 16.00 < > D3D Assembly Statistics

Performance statistics for different GPUs

### AMD IL to GPU ISA

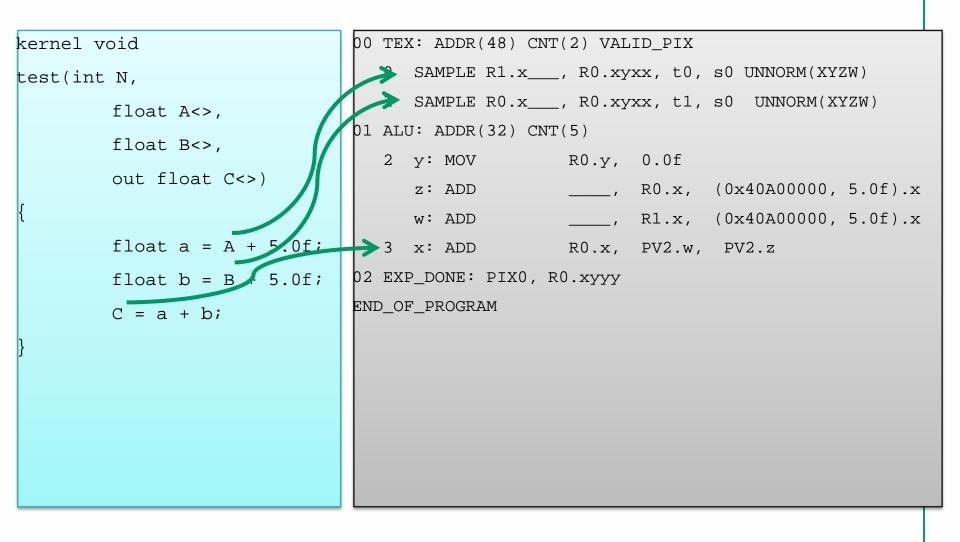

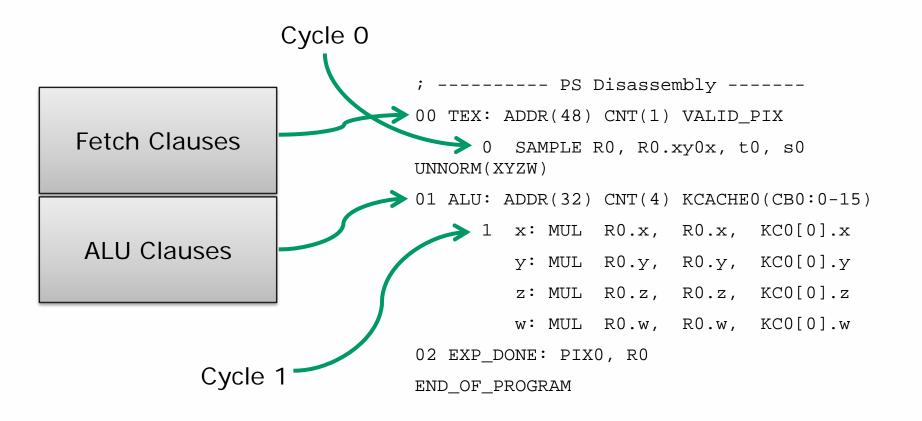

### AMD GPU ISA - Program Structure

- ISA Program consists of set of Instruction Clauses

- ALU Clauses

- TEX Clauses

- ISA Maps directly to the underlying hardware

- Computational Core consists of 5-way ALU units

- ALU Clause consists of one or more ALU Instruction Groups

- ALU Instruction Group consists of up-to 5 ALU instructions

- Represented by x, y, z, w, t

- TEX Clauses perform memory read operations

- Texture mapping in 3D graphics

- Additional Flags are used for compute-specific features

### AMD GPU ISA - Program Example

### AMD GPU ISA

- Reveals Information on

- Actual number of ALU cycles in kernel

- Data Dependencies

- ALU utilization

- Does not reveal Information on

- Total number of cycles for execution

- Memory access latencies are not accounted for

### AMD GPU ISA - Program Structure

### **Important Tokens**

- **R#** 128-bit GPRs

- **KCACHE#** GPU Constant Cache

- **SAMPLE** Memory Read Operation

- **F\_TO\_I** Floating point to Integer conversion

- **LOOP\_DX10** DX10-style **for** loop

### **Q&A and Recap**

- CAL Kernel Programming Interfaces

- Brook+

- HLSL

- AMD IL

- AMD GPU ISA